So Monday at work I successfully pulled a prank on the designer for the part that is currently occupying the majority of my time. Concept, planning, and execution took about two weeks or so as I had to fit this little side project in around my real work obviously. Ever since the part’s inception this designer had been claiming it was perfectly designed and any errors were clearly the fault of me, the Applications Engineer. He wasn’t being mean or anything, this sort of good-natured rivalry is pretty common between the Apps and Design departments at work, but being that this is my first part as lead apps since starting a year ago meant I got some extra abuse. I figured it would be a good idea to go on the offensive and show everyone I wasn’t such an easy target. My boss, who’s been good friends with the designer for a long time now, thought it would be pretty funny and approved the gag, eager to see how it would play out.

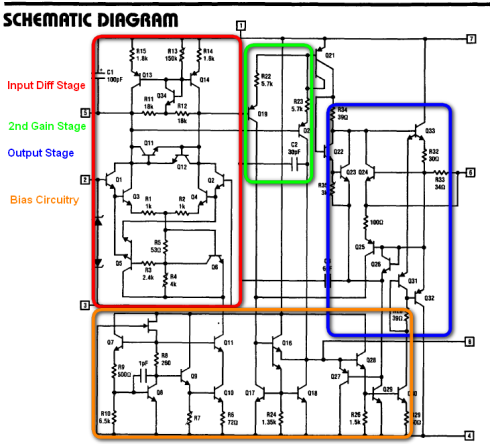

The part is a single phase buck regulator meant for Vcore applications in laptops and ultrabooks. Vcore means that the regulator provides the main voltage rail to the processor, specifically an Intel one in this case as AMD and other processors have different power requirements. My goal was to somehow screw with the regulator, cause the output voltage to glitch and go out of spec, and convince the designer this was a silicon bug and not a board issue. After a little brain storming I came up with the following circuit which could be cobbled together out of various parts in the lab:

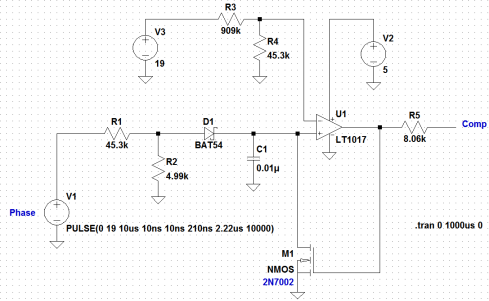

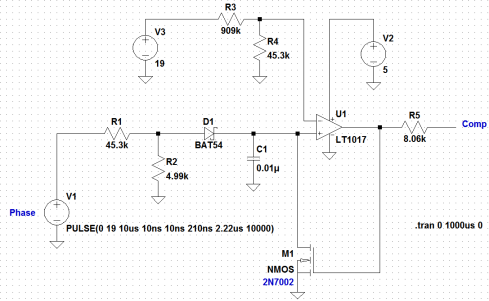

My Prank Circuit

Without diving down the rabbit hole that is regulator compensation, the comp pin of any buck converter is the output of an error amplifier which connects to a networks of passives going back to its negative terminal (the Feedback pin) and is part of the control loop used to keep the output voltage stable and well-regulated. My circuit would periodically drive this pin away from its steady state operating point. This disturbance would propagate through the chip and result in a noticeable glitch on the output voltage until the compensation loop could regain control and bring the output voltage back into spec.

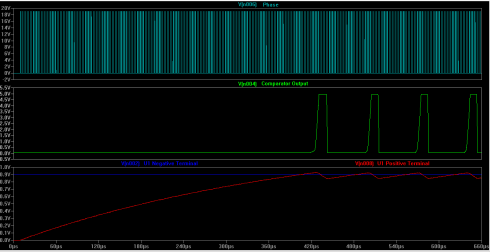

As phase switches merrily along at the frequency and duty cycle set by the controller it gets divided down by R1 and R2. When phase is high the output of this voltage divider is enough to forward bias the diode and cause current to flow into C1 for a brief period before going low again. C1, which also connects to the positive input comparator U1, charges over time and when the voltage across the cap gets to be higher than the reference voltage present on the comparator’s negative input the comparator’s output swings to 5V. When U1’s output goes high two things happen. One, comp is driven away from steady state through R5 and two, the gate of M1 goes high which discharges C1 below the reference voltage starting the cycle over again.

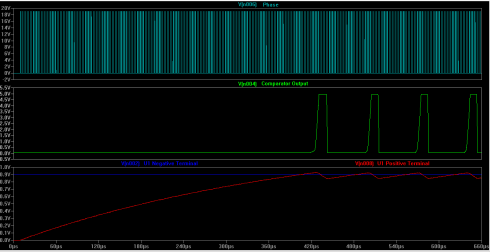

Prank Circuit Sim Results (Click to view properly)

There really wasn’t much thought process behind the component values in my circuit; they were determined through trial and error in simulation. I didn’t care how often the circuit would trigger, only that it did and the disturbances it caused would appear on Vout. One of my only goals was to ensure that the resistor dividers wouldn’t draw enough current to interfere with the normal operation of the regulator and cause it not to start up. My second goal was to “break” the regulator just enough to cause concern but not enough to trigger any of various over voltage, current, or temperature protections built into the chip. This is why R5 had to be added; without it comp was driven too hard and the part simply shutdown (there’s no fun in that).

With the circuit idea solidified I headed into the lab to jury rig it into place underneath one of the eval boards. It was a messy hour after work one day, but I successfully placed each component and wired in the various signals and voltages from all across the board. Once things got going, there would be so many cables and probes attached to the board I knew it wouldn’t get turned over until I was ready to reveal what I’d done.

Holding my breath I powered up the board after making all the necessary modifications. Surprisingly enough it worked! I hadn’t made any disastrous mistakes when wiring it all up and the resulting waveforms basically match with my sims. All that was needed was some tweaking of R5 to find the right value and I was ready for action.

Cutting to Monday morning, I spent a little time taking scope captures of a good board and my doctored eval board. These were placed in a quick report which I shot off to my boss and the designer right after lunch. To add to the joke I took my clean scope caps using a part from an old rev of silicon and explained how the “bug” was only seen in the latest version of the chip. This caused the initial spark of concern in the designer as we’re currently waiting on a new rev of the chip to arrive from the fab and it was too late to make any changes. After getting some tests to run and tweaks to try, I actually went into the lab and did them! For one I was curious to see if any of them could actually fix the error (they didn’t) and secondly, this designer is pretty hands on and likes to come out to Apps Lab quite often. I knew that if he came out to see the glitch on the bench and none of his changes were made he would get suspicious. Fortunately, or unfortunately, other obligations kept him away for the day and he never came out to see the problem until the end of the day.

After running the initial list of tests the designer gave me I had a flash of brilliance that really threw him for a loop. I took a series of scope shots at each of the four switching frequencies our part could run at and varied the value of R5 at each one. Now I had created a problem that went away as switching frequency increased and could explain why we hadn’t seen this issue before as the majority of our testing had taken place at high frequency up until this point! Bingo.

By the end of the day, the designer was pretty much stumped. He’d done an initial check of his schematics, couldn’t spot an obviously fault he made, but thought it was a mistake somewhere in the core of the modulator. He told me that at this point he essentially resigned himself to hoping the new version of the chip came out okay and whatever changes he made would happen to fix this (remember it’s too late to make changes now as the part’s being fabricated).

Right afterwards I called him into the lab saying I’d found something interesting and he should come take a look. When I showed him the circuit on back of the board he didn’t get it at first. He asked why all this crap was added and what did it fix? I couldn’t hold back anymore and broke out in a smile and said that I just wanted to mess with him. Slowly realization dawned on him and he started laughing as did my boss and a few other guys in the lab who were in on the joke.

In the end the designer took it really well and thought it was pretty funny. He told my boss to give me more work as clearly I didn’t have enough to do since I could pull these elaborate pranks but mostly he just laughed. I now owe him a round or two the next time a bunch of us go out after work but that’s a price I’m more than willing to pay all things considered. In the end I caused him just enough trouble so he started to sweat but not enough to take him away from any real tasks he had to get done. A well executed prank overall in my opinion. Surely, there’s no way this will every come back to haunt me right?